### NORTHWESTERN UNIVERSITY

Developing and Understanding Materials Processing-Property Relationships for Carbon

Nanotube Electronics

### A DISSERTATION

# SUBMITTED TO THE GRADUATE SCHOOL IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

for the degree

### DOCTOR OF PHILOSOPHY

Field of Materials Science and Engineering

By

William A. Gaviria Rojas

EVANSTON, ILLINOIS

June 2020

© Copyright by William A. Gaviria Rojas 2020

All Rights Reserved

#### ABSTRACT

Developing and Understanding Materials Processing-Property Relationships for Carbon

Nanotube Electronics

#### William A. Gaviria Rojas

The commercial success of personal computing has led to the rapid creation and proliferation of diverse electronic systems including desktops, laptops, tablets, mobile devices, and embedded systems. For the past five decades, silicon has served as the base material for computing electronics. However, with increasing demand for unconventional electronics (e.g., ultrathin flexible wearables), new computing platforms are required that meet increasingly diverse mechanical, electronic, and functional requirements. Conventional silicon integrated circuit technology faces significant challenges in meeting these demands due to its limited mechanical flexibility, high temperature processing, and scaling limitations. Emerging alternative computing platforms based on other crystalline semiconductors suffer from similar limitations. Consequently, next-generation electronics necessitates the exploration of radically different electronic materials.

Single-walled carbon nanotubes (SWCNTs) are among the most promising and highly studied nanoelectronic materials. Due to their small size, solution-processability, chemical stability, and chirality-dependent optoelectronic properties, SWCNTs offer a number of unique advantages and are compatible with the complex requirements of future electronic devices. Recent advances in post-processing methods have allowed SWCNTs to be used as semiconducting channels in diverse settings including charge transport devices, optical emitters and detectors, and chemical sensors. With this tunable functionality, a wide range of SWCNT-based electronic applications have been realized, such as printed digitial logic and complementary metal-oxide-

semiconductor (CMOS) field-effect transistors (FETs). Despite this progress, most applications realized to date have largely focused on digital logic, and demonstrations of other key logic and analog functions remain largely unexplored. Moreover, silicon electronics are often used to perform these functions, further limiting the impact of SWCNT-based devices in practical electronic systems. Therefore, SWCNT-based electronics capable of performing these key functions must be realized to fully exploit the potential of solution-processed SWCNTs in emerging electronics. To this end, work presented in this dissertation focuses on the development of materials processing methods and their impact on SWCNT device properties. With this understanding of processing-property relationships, this work demonstrates SWCNT devices with novel function and performance in two key applications, overcoming fundamental challenges in the development SWCNT-based security and sensing technologies.

Innovative materials processing and device operation are at the core of this thesis and have led to the development of the first true random number generator based on a solution-processed semiconductor. Processing optimization of charge transport through tunable doping, encapsulation and transistor design enabled the realization of low-power, complementary SWCNT static random access memory (SRAM) cells. Further characterization of device operation under dynamic biasing conditions allowed for the development of biasing strategies to operate these SWCNT SRAM cells as random bit generators through digitization of thermal noise. This work shows that this approach requires minimal computational overhead to produce highly random bit streams, as is confirmed through a series of rigorous tests including the National Institute of Standards and Technology (NIST) randomness statistical test suite (STS) and the TestU01 battery tests. This thesis work thus overcomes a key application-specific challenge to low cost, flexible security electronics by demonstrating a ubiquitous security primitive using a solution-processed semiconductor. In turn, this provides a path for improving security in the rapidly growing global network of interconnected electronic and sensing devices.

Further innovative transistor design and understanding of material processing-property relationships led to the development of a novel ohmic-contact-gated transistor (OCGT) using solution-processed SWCNTs. Through the development of a novel self-aligned photolithography technique and processing optimization of components critical in charge transport (i.e., contacts and channel), a key advantage of the OCGT device geometry is realized through gating of the semiconducting channel with both the bottom gate and top contact electrode without the need of additional terminals beyond the conventional gate-source-drain configuration. In turn, this novel transistor design enables unprecedented levels of output current saturation in short channel limits (i.e., channel lengths < 300 nm) using atomically thin semiconductors without compromising the output current drive. Solution-processed SWCNT random networks are used to implement OCGTs that mitigate short channel effects to achieve low output conductance with high output current levels, overcoming the tradeoff relationship that is typically observed in conventional field-effect transistors FETs. These SWCNT OCGTs are then used in common-source amplifiers to attain the highest output current density and length-scaled signal gain to date for amplifiers based on solution-processed semiconductors, overcoming a key challenge in the development of practical sensing technologies. The utility and robustness of these amplifiers is further demonstrated by amplifying a number of analog biological signals from sensors commonly found in Internet of Things (IoT) and medical devices. Because the facile OCGT fabrication design can be generalized to other semiconducting nanomaterials, this thesis work has wide-ranging implications for solution-processed analog electronics.

#### **ACKNOWLEDGEMENTS**

First and foremost, thanks be to God for blessing me with such an amazing opportunity, surrounding me with my loved ones and giving me the strength to run as far as I've been able to run in my race. Your continued presence, love and support is more than I deserve, and I will use my abilities to bring these same blessings to others.

Second, I dedicate this PhD to my family and my girls. Your constant support and love at home is the foundation of all my achievements. I would not be anywhere near where I am today if it wasn't for all of you. Love you all beyond what words can describe.

I also want to thank the United States. My family may not have been born here, but you gave us a fresh start when we needed it most. We are now far better off that we would have imagined with an even brighter future going forward thanks to the amazing opportunities you've given us. More importantly, you gave us a new home. My sincerest thank you to this amazing country.

Thank you Mark for all that you've done. At a time when I almost dropped out of pursuing my PhD, you took me in and gave me a new research home. You showed me what it means to be researcher, a leader and a mentor. Your advice was invaluable in shaping how I approach both research and success in general. Thank you for all the lessons you've taught me. I will carry these on for the rest of my career.

A sincerest thank you to all of my committee members (Prof. David Seidman, Prof. Robert Chang, and Prof. Jie Gu) for your time and your support during this final stage of PhD journey.

A sincerest thank you to all my early supporters, Prof. Tomas Palacios, Prof. David Perreault, Prof. Stephen Campbell, and Prof. Mildred Dresselhaus. Your mentorship, research direction and support were invaluable in my undergraduate and graduate journey. A special thank you to Prof. Mildred Dresselhaus, who gave me a chance to prove myself in research when I was just a sophomore, and whose intellectual prowess was always a source of inspiration. May she rest in peace with the Lord.

A sincere thank you to Dean Karpus, Dean McBride, Allen and Alan for all of your support in helping me transition to a healthier environment. I am certain I would have never finished my PhD without your help.

A sincere thank you to Prof. Chris Kim, and all my other collaborators for their support in the realization of my research projects.

A sincere thank you to the NSF Graduate Research Fellowship Program, the GEM Engineering PhD fellowship, and MIT Lincoln Laboratory for their financial support throughout my PhD.

I also want to thank all of the following: Mike and Julian, whose initial mentorship and friendship were invaluable in my transition to the Hersam group. Hersam group members, mentors, mentees and friends – thank you all for all the mentorship, discussions, laughs, karaoke nights and for just making this the best research group in more ways than just our running ability (#5kchampions). Bruce, the hidden jewel of graduate engineering, whose constant support and friendship was a shining light in my graduate path. Kristen, for believing in me and giving me a chance to share Illuminate with as many students as I could. Royce and my EE folks, who were always there for me when I needed guidance and a spare transistor. Lisa, Dan and all the folks at the pantry, thank you for your friendship and for everything you do. All of my friends at EGC, thank you for your friendship and for the amazing community you have. Last but not least, my long-time friends, whose friendship I always cherish.

### LIST OF ABBREVIATIONS

| 0D                             | Zero-dimensional                                   |

|--------------------------------|----------------------------------------------------|

| 1D                             | One-dimensional                                    |

| 2D                             | Two-dimensional                                    |

| 3D                             | Three-dimensional                                  |

| ADC                            | Analog-to-digital converter                        |

| AFM                            | Atomic force microscopy                            |

| AI                             | Artificial intelligence                            |

| Al <sub>2</sub> O <sub>3</sub> | Aluminum oxide, alumina                            |

| ALD                            | Atomic layer deposition                            |

| AMOLED                         | Active-matrix organic light-emitting diode display |

| ATPE                           | Aqueous two-phase extraction                       |

| BFBD                           | Barrier-free bipolar-diode                         |

| BJT                            | Bipolar junction transistor                        |

| BL                             | Bitline                                            |

| BV                             | Benzyl viologen                                    |

| CD                             | Circular dichroism                                 |

| CMOS                           | Complementary metal-oxide-semiconductor            |

| CNT                            | Carbon nanotube                                    |

| CTOLED                         | Color-tunable organic light-emitting diode         |

| CVD                            | Chemical vapor deposition                          |

| DC                             | Direct current                                     |

| DGU              | Density gradient ultracentrifugation |

|------------------|--------------------------------------|

| DOPA             | 3,4-dihydroxyphenylalanine           |

| DPV              | Differential pulse voltammetry       |

| DX               | Dextran                              |

| EBL              | Electron beam lithography            |

| ECG              | Electrocardiogram                    |

| EL               | Electroluminescence                  |

| EMG              | Electromyography                     |

| EPSC             | Excitatory post-synaptic current     |

| FESA             | Floating evaporative self-assembly   |

| FET              | Field-effect transistors             |

| FFT              | Fast Fourier transform               |

| FMN              | Flavin mononucleotide                |

| FWHM             | Full width at half maximum           |

| GC               | Gel chromatography                   |

| GCE              | Glassy carbon electrode              |

| GND              | Ground                               |

| g <sub>m</sub>   | Transconductance                     |

| go               | Output conductance                   |

| hBN              | Hexagonal boron nitride              |

| HfO <sub>2</sub> | Hafnium (IV) oxide, hafnia           |

| IC               | Integrated Circuit                   |

| I <sub>DS</sub>  | Drain current                        |

|                  |                                      |

| I <sub>DS,max</sub>              | Maximum drain current                              |

|----------------------------------|----------------------------------------------------|

| I <sub>DS</sub> -V <sub>DS</sub> | Output                                             |

| $I_{DS}$ - $V_{GS}$              | Transfer                                           |

| I <sub>off</sub>                 | Off current                                        |

| I <sub>on</sub>                  | On current                                         |

| IoT                              | Internet of Things                                 |

| IR                               | Infrared                                           |

| JNFET                            | Junction-less nanowire field-effect transistor     |

| L                                | Field-effect transistor channel length             |

| $MoS_2$                          | Molybdenum disulfide                               |

| m-SWCNT                          | Metallic single-walled carbon nanotube             |

| NIST                             | National Institute of Standards and Technology     |

| NMOS                             | n-channel metal-oxide-semiconductor                |

| NMP                              | N-methyl-2-pyrrolidone                             |

| NMPI                             | 4-(N-hydroxycarboxamido)-1-methylpyridinium iodide |

| O <sub>2</sub>                   | Oxygen                                             |

| OCGT                             | Ohmic-contact-gated transistor                     |

| OLED                             | Organic light-emitting diode                       |

| PAM                              | Polyacrylamide                                     |

| PCz                              | Poly[9-(1-octylonoyl)-9H-carbazole-2,7-diyl]       |

| PDLC                             | Polymer-dispersed liquid crystals                  |

| PDMS                             | Polydimethylsiloxane                               |

| PECVD                            | Plasma-enhanced chemical vapor deposition          |

|                                  |                                                    |

| Poly(ethylene glycol)                                       |

|-------------------------------------------------------------|

| Polyethylene naphthalate                                    |

| Poly(ethylene terephthalate)                                |

| Poly[(9,9-dioctylfluorenyl-2,7-diyl)-alt-co-(6,6'-[2,2'-    |

| bipyridine])]                                               |

| Photoluminescence                                           |

| Poly(methyl methacrylate)                                   |

| p-channel metal-oxide-semiconductor                         |

| Poly(methyl silsesquioxane)                                 |

| Photoplethysmogram                                          |

| Pressure-sensitive rubber                                   |

| Physically unclonable function                              |

| Polyvinyl alcohol                                           |

| Poly(vinylphenol)                                           |

| Roll-to-roll                                                |

| Relative humidity                                           |

| Reactive ion etching                                        |

| Ring oscillator                                             |

| Output resistance                                           |

| Resistive random-access memory                              |

| Self-aligned capillary-assisted lithography for electronics |

| Styrene-ethylene-butadiene-styrene                          |

| Scanning electron microscope                                |

|                                                             |

| SGT             | Source-gated transistor                      |

|-----------------|----------------------------------------------|

| SMU             | Source-measurement unit                      |

| SNN             | Spiking neural network                       |

| SPE             | Single photon emission                       |

| SRAM            | Static random-access memory                  |

| SS              | Subthreshold swing                           |

| ss-DNA          | Single-stranded DNA                          |

| STDP            | Spiking-time dependent plasticity            |

| STS             | Statistical test suite                       |

| SWCNT           | Single-walled carbon nanotube                |

| s-SWCNT         | Semiconducting single-walled carbon nanotube |

| TDMAH           | Tetrakis(dimethylamido)hafnium(IV)           |

| TMAI            | Trimethylaluminum                            |

| TEM             | Transmission electron miscroscope            |

| TID             | Total ionization dose                        |

| TFT             | Thin-film transistor                         |

| TRNG            | True random number generator                 |

| UV              | Ultraviolet                                  |

| VCO             | Voltage-controlled oscillator                |

| V <sub>DS</sub> | Drain-source voltage                         |

| $V_{DD}$        | Supply voltage                               |

| VEGT            | Vertical electrolyte-gated transistor        |

| $V_{GS}$        | Gate-source voltage                          |

| V <sub>IN</sub>  | Input voltage                         |

|------------------|---------------------------------------|

| VLSI             | Very-large-scale-integration          |

| V <sub>OUT</sub> | Output voltage                        |

| V <sub>TH</sub>  | Threshold voltage                     |

| W                | Field-effect transistor channel width |

| WL               | Wordline                              |

| $\mu_{	ext{FE}}$ | Field-effect mobility                 |

Dedicated to my family and my girls

# TABLE OF CONTENTS

| ABSTRACT                                                             |     |

|----------------------------------------------------------------------|-----|

| ACKNOWLEDGEMENTS                                                     | 6   |

| LIST OF ABBREVIATIONS                                                |     |

| LIST OF FIGURES                                                      | 17  |

| LIST OF TABLES                                                       |     |

| Chapter 1: Introduction to carbon nanotubes                          |     |

| 1.1 SWCNTs in modern electronics                                     |     |

| 1.2 SWCNT electronic properties                                      |     |

| 1.3 SWCNT direct growth                                              |     |

| 1.4 SWCNT post-processing purification                               |     |

| Chapter 2: Carbon nanotube electronic devices                        |     |

| 2.1 Electronic applications of semiconducting SWCNTs                 |     |

| 2.1.1 Flexible smart devices                                         |     |

| 2.1.2 Planar high-performance computing                              | 52  |

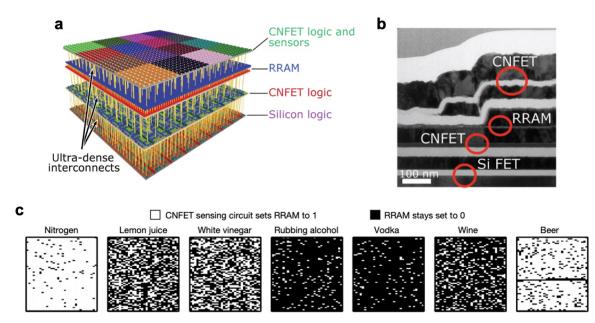

| 2.1.3 Three-dimensional monolithic logic-memory integration          | 65  |

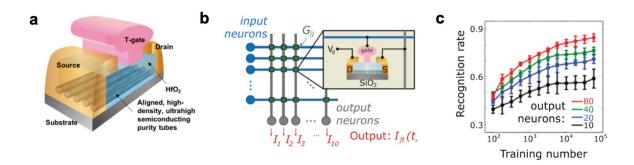

| 2.1.4 Neuromorphic computing                                         | 68  |

| 2.2. Electronic applications of chirality-enriched SWCNTs            | 71  |

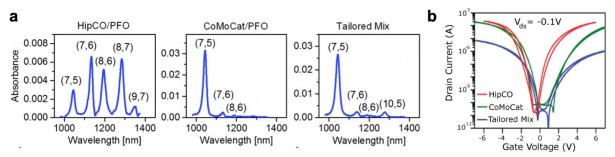

| 2.2.1 Charge transport in FETs                                       | 71  |

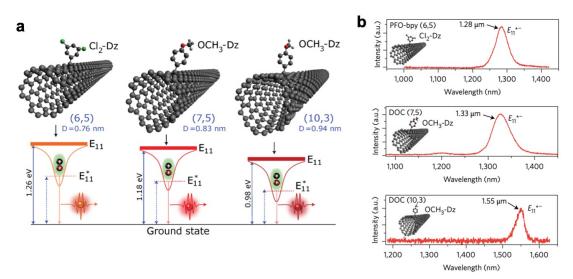

| 2.2.2 Optical emitters                                               | 74  |

| 2.2.3 Photodetectors                                                 | 82  |

| 2.2.4 Optoelectronic integrated circuits                             | 84  |

| 2.3 Progress in enantiomerically-pure SWCNTs                         | 87  |

| Chapter 3: Carbon nanotube true random number generator              |     |

| 3.1 Random number generators in security applications                |     |

| 3.2 Processing optimization for the fabrication of SWCNT SRAM cells  |     |

| 3.3 Bit generation through tunable doping, encapsulation and biasing |     |

| 3.4 Tuning of output bit streams                                     | 103 |

| 3.5 Randomness testing                                               | 108 |

| Chapter 4: Carbon nanotube ohmic-contact-gated transistors           | 117 |

| 4.1 Challenges in solution-processed short-channel amplifiers        |     |

| 4.2 Fabrication of SWCNT OCGTs                                       | 120 |

| 4.3 Performance of SWCNT OCGTs                                       | 125 |

|                                                               | 16  |

|---------------------------------------------------------------|-----|

| 4.4 SWCNT OCGT-based amplifiers for practical sensing systems |     |

| Chapter 5: Conclusion and Outlook                             |     |

| 5.1 Summary                                                   |     |

| 5.2 Synaptic transistors for neuromorphic computing           |     |

| 5.3 Electrically-driven single-photon emitters                |     |

| 5.4 General outlook                                           |     |

| REFERENCES                                                    |     |

| VITA                                                          | 190 |

# **LIST OF FIGURES**

| Figure 1.1   Unsorted SWCNTs                                         |    |

|----------------------------------------------------------------------|----|

| Figure 1.2   SWCNTs sorted by electronic type                        |    |

| Figure 1.3   SWCNTs sorted by chirality                              |    |

| Figure 1.4   SWCNTs sorted by chirality and handedness.              |    |

| Figure 1.5   SWCNT growth using molecular templates                  |    |

| Figure 1.6   SWCNT growth using electro-renucleation                 |    |

| Figure 1.7   SWCNT growth using microwave-assisted regeneration      |    |

| Figure 1.8   SWCNT sorting using dielectrophoretic assembly.         |    |

| Figure 1.9   SWCNT sorting using polymer-wrapping                    |    |

| Figure 1.10   SWCNT sorting using ATPE.                              |    |

| Figure 1.11   SWCNT sorting using DGU                                |    |

| Figure 1.12   SWCNT sorting using gel chromatography                 |    |

| Figure 2.1   Stretchable temperature sensing circuit.                |    |

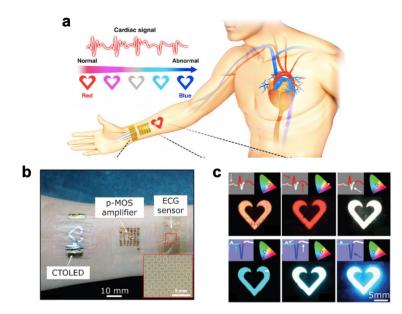

| Figure 2.2   Wearable cardiac monitoring system                      |    |

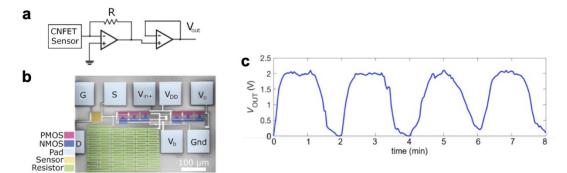

| Figure 2.3   Integrated breath sensor with an analog sub-system.     | 59 |

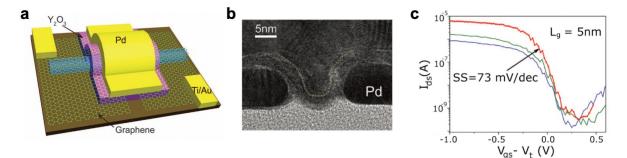

| Figure 2.4   SWCNT FET scaled down to a 5 nm gate                    |    |

| Figure 2.5   3D monolithic integrated system.                        |    |

| Figure 2.6   SWCNT synaptic transistors for neuromorphic computing   |    |

| Figure 2.7   Charged transport of mixed SWCNT networks               |    |

| Figure 2.8   Tunable defect-state emission in monochiral SWCNTs      |    |

| Figure 2.9   Electrically-pumped SWCNT emitter.                      |    |

| Figure 2.10   Microcavity-integrated SWCNT photodetector.            |    |

| Figure 2.11   Optoelectronic logic gate                              |    |

| Figure 2.12   SWCNT enantiomeric enrichment using ATPE               | 89 |

| Figure 2.13   SWCNT enantiomeric enrichment using DGU.               |    |

| Figure 2.14   SWCNT enantiomeric enrichment using gel chromatography |    |

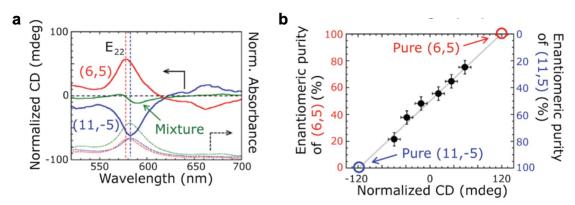

| Figure 2.15   SWCNT enantiomeric purity characterization using FNM   |    |

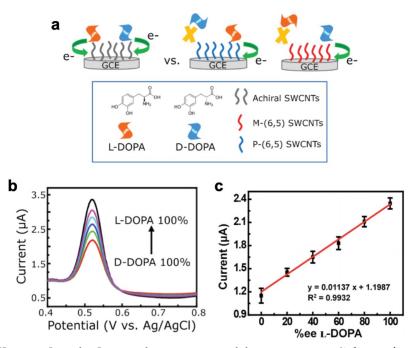

| Figure 2.16   Electrochemical enantiomer recognition sensor          |    |

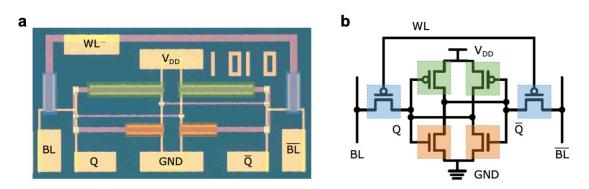

| Figure 3.1   SWNT complementary SRAM cell.                           |    |

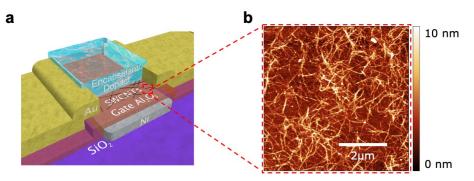

| Figure 3.2   SWNT TFT in SRAM cell                                   |    |

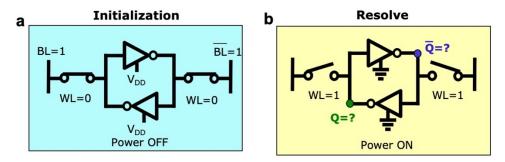

| Figure 3.3   SRAM operation as a bit generator.                      |    |

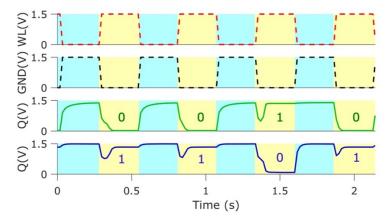

| Figure 3.4   SRAM bit generator output                               |    |

| 18<br>Times 2.5   Sharry Lastart from SPAM1 it an article                                 |

|-------------------------------------------------------------------------------------------|

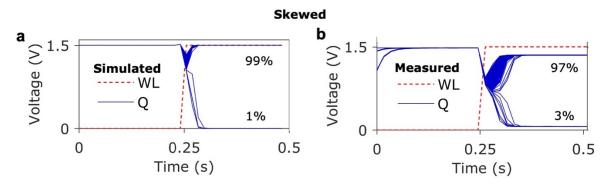

| Figure 3.5   Skewed output from SRAM bit generation                                       |

| Figure 3.6   Balanced output from SRAM bit generation                                     |

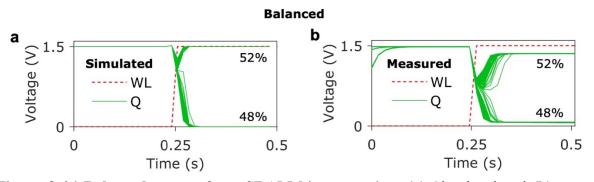

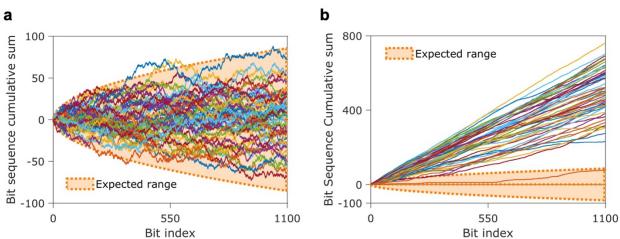

| Figure 3.7   Bitmaps of output from SRAM bit streams                                      |

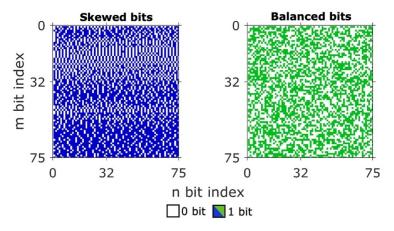

| Figure 3.8   Average bit values of 20-bit segments from bit generation                    |

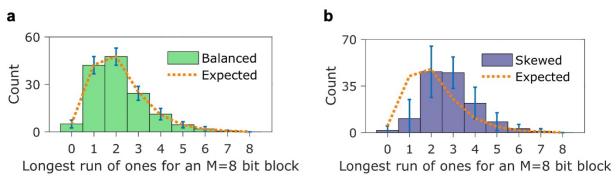

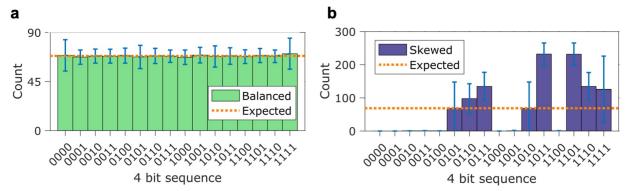

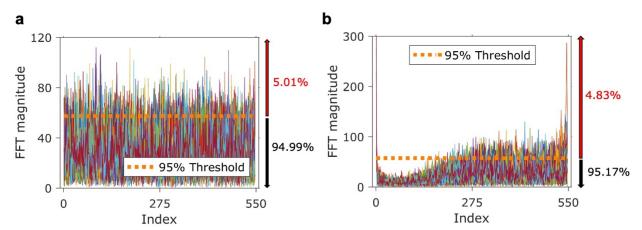

| Figure 3.9   NIST STS frequency test 109                                                  |

| Figure 3.10   NIST STS longest run of ones test                                           |

| Figure 3.11   NIST STS serial test                                                        |

| Figure 3.12   NIST STS FFT test 111                                                       |

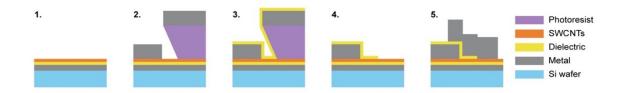

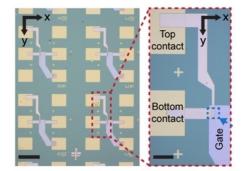

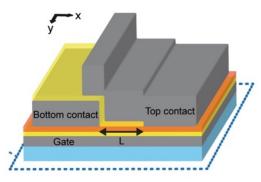

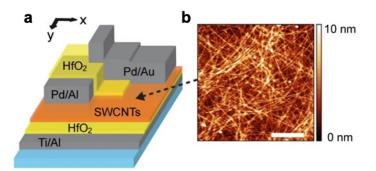

| Figure 4.1   SWCNT OCGT fabrication 120                                                   |

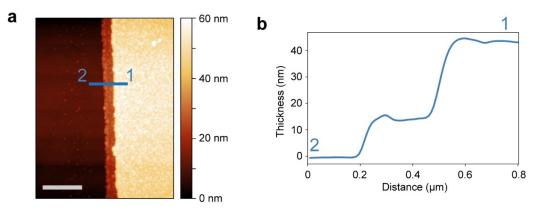

| Figure 4.2   Characterization of dielectric extension 121                                 |

| Figure 4.3   SWCNT OCGT lateral view                                                      |

| Figure 4.4   SWCNT OCGT device schematic                                                  |

| Figure 4.5   SWCNT OCGT materials selection                                               |

| Figure 4.6   Performance of a SWCNT OCGT – Linear transfer                                |

| Figure 4.7   Performance of a SWCNT OCGT – Log-linear transfer                            |

| Figure 4.8   Histogram of SWCNT OCGT ON/OFF ratio performance                             |

| Figure 4.9   Histogram of SWCNT OCGT on-current performance                               |

| Figure 4.10   Performance of a SWCNT OCGT – Linear output                                 |

| Figure 4.11   Histogram of SWCNT OCGT maximum output current performance                  |

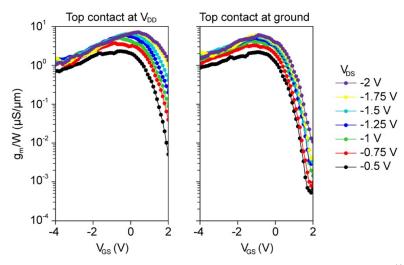

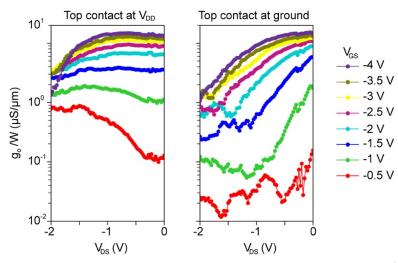

| Figure 4.12   Performance of a SWCNT OCGT – transconductance and output conductance.      |

| Figure 4.13   Histogram of SWCNT OCGT output conductance and transconductance performance |

| Figure 4.14   SWCNT OCGT transconductance characterization                                |

| Figure 4.15   SWCNT OCGT output conductance characterization                              |

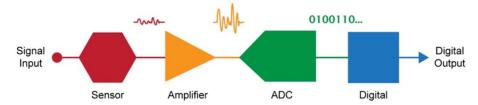

| Figure 4.16   Signal acquisition overview                                                 |

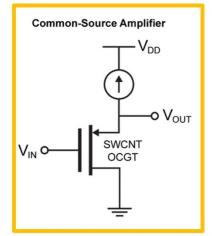

| Figure 4.17   SWCNT OCGT-based amplifier                                                  |

| Figure 4.18   Characterization of signal gain in SWCNT OCGT-based amplifier               |

| Figure 4.19   Performance of amplifiers based on solution-processed semiconductors        |

| Figure 4.20   Amplification of EMG sensor signal                                          |

| Figure 4.21   Amplification of PPG sensor signal                                          |

| Figure 4.22   Amplification of accelerometer sensor signal                                |

| Figure 5.1   SWCNT Synaptic transistor                                                    |

| Figure 5.2   Spiking neural network using STDP                                            |

| Figure 5.3   Results of trained spiking neural network.                  | 19<br>150 |

|--------------------------------------------------------------------------|-----------|

| Figure 5.4   Excitation-emission spectra of polymer-wrapped (6,5) SWCNTs |           |

| Figure 5.5   Exciton PL in diazonium-functionalized (6,5) SWCNTs         | 152       |

| Figure 5.6   Next-generation SWCNT-based computing system                | 157       |

### LIST OF TABLES

| Table 3.1   Bits collected from SWCNT SRAM devices following post-processing | . 106 |

|------------------------------------------------------------------------------|-------|

| Table 3.2   Summary of NIST STS results                                      | . 114 |

| Table 3.3   Summary of TestU01 results                                       | . 115 |

| Table 4.1   Median values of key performance metrics for 67 SWCNT OCGTs      | . 134 |

|                                                                              |       |

Chapter 1: Introduction to carbon nanotubes

For the past half century, silicon has served as the primary material platform for integrated circuit technology. However, the recent proliferation of non-traditional electronics, such as wearables, embedded systems, and low-power portable devices, has led to increasingly complex mechanical and electrical performance requirements. Among emerging electronic materials, single-walled carbon nanotubes (SWCNTs) are promising candidates for next-generation computing as a result of their superlative electrical, optical, and mechanical properties. Moreover, their chirality-dependent properties enable a wide range of emerging electronic applications including sub-10 nm complementary field-effect transistors, optoelectronic integrated circuits, and enantiomer-recognition sensors. In this section, we review recent progress in SWCNT-based computing devices, with an emphasis on the relationship between chirality enrichment and electronic functionality. In particular, we highlighting chirality-dependent SWCNT properties and chirality enrichment methods, summarizing the range of computing applications that have been demonstrated using SWCNTs to date.

#### **1.1 SWCNTs in modern electronics**

The commercial success of personal computing has led to the rapid creation and proliferation of diverse electronic systems including desktops, laptops, tablets, mobile devices, and embedded systems. For the past five decades, silicon has served as the base material for computing electronics.<sup>1</sup> However, with increasing demand for unconventional electronics (e.g., ultrathin flexible wearables), new computing platforms are required that meet increasingly diverse mechanical,<sup>2</sup> electronic,<sup>3,4</sup> and functional requirements.<sup>5</sup> Conventional silicon integrated circuit technology faces significant challenges in meeting these demands due to its limited mechanical flexibility, high temperature processing, and scaling limitations. Emerging alternative computing

platforms based on other crystalline semiconductors suffer from similar limitations. Consequently, next-generation computing necessitates the exploration of radically different electronic materials.

Single-walled carbon nanotubes (SWCNTs) are among the most promising and highly studied nanoelectronic materials. Due to their small size,<sup>6,7</sup> solution-processability,<sup>8</sup> chemical stability,<sup>9</sup> and chirality-dependent optoelectronic properties,<sup>10</sup> SWCNTs offer a number of unique advantages and are compatible with the complex requirements of future computing devices. Recent advances in chiral enrichment of polydisperse SWCNTs<sup>8,10</sup> have allowed their use as semiconducting channels in diverse settings including charge transport devices,<sup>2</sup> optical emitters and detectors,<sup>11,12</sup> and chemical sensors.<sup>2,3,13,14</sup> With this tunable functionality, a range of SWCNT-based computing applications have been realized, such as printed digital logic,<sup>15</sup> sub-10 nm complementary metal-oxide-semiconductor (CMOS) field-effect transistors (FETs),<sup>16</sup> neuromorphic devices,<sup>17</sup> single-photon emitters,<sup>18</sup> and enantiomer-recognition sensors.<sup>14</sup>

In this section, we discuss recent advances in SWCNT-based computing technologies that process, manage, and communicate information, with an emphasis on the enabling role of chiral enrichment. Section 1.2 defines the different levels of chiral enrichment. Sections 1.3 and 1.4 describe direct growth methods and post-processing purification of SWCNTs for electronic-type and monochiral enrichment. Section 2.1 discusses applications of electronic-type-enriched SWCNTs such as wearables, highly-scaled FETs, three-dimensional (3D) logic-memory integration, and neuromorphic devices. Section 2.2 outlines applications of monochiral-enriched SWCNTs including monochiral FETs, optical emitters, photodetectors, and optoelectronic integrated circuits (ICs). Finally, Section 2.3 considers recent progress towards enantiomerically-pure SWCNTs.

#### **1.2 SWCNT electronic properties**

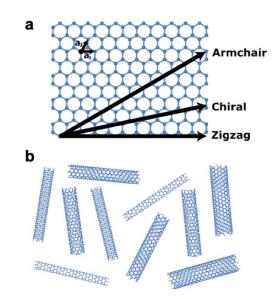

SWCNTs and graphene are carbon allotropes consisting of sp<sup>2</sup>-bonded carbon atoms. While graphene consists of a planar layer of carbon atoms in a honeycomb lattice arrangement, a SWCNT can be thought of as a single sheet of graphene rolled to form a seamless, hollow cylinder. Most properties of a SWCNT are determined by the rolling direction with respect to the graphene lattice, which is referred to as the SWCNT chiral vector. As shown in Figure 1.1, the chiral vector is defined with respect to the basis vectors ( $\mathbf{a}_1$ ,  $\mathbf{a}_2$ ) such that each SWCNT structure is identified by a pair of chiral indices (*n*,*m*). The SWCNT structures shown in Figure 1.1 are generated using the TubeGen 3.4 web interface.<sup>19</sup> Typically, SWCNTs have a diameter of less than 2 nm, with lengths in the range of 1-2 µm. Given their high aspect ratios, SWCNTs are commonly classified as one-dimensional nanostructures.

**Figure 1.1** | **Unsorted SWCNTs. a**, Diagram of a graphene sheet with basis vectors (a1, a2) and common chiral vectors used to define SWCNTs. **b**, Conceptual illustration of as-produced raw, unsorted SWCNTs with numerous chiralities. These SWCNT structures were generated using the TubeGen 3.4 web interface<sup>.19</sup> Reproduced with permission.<sup>20</sup> Copyright 2020, Wiley-VCH Verlag GmbH & Co. KGaA, Weinheim.

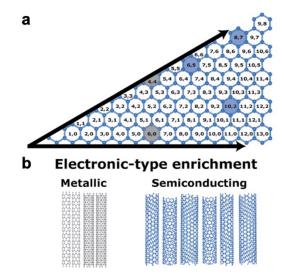

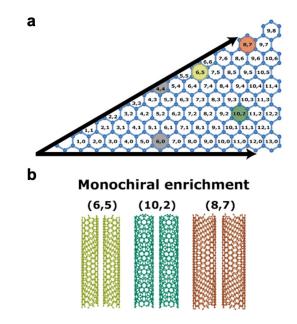

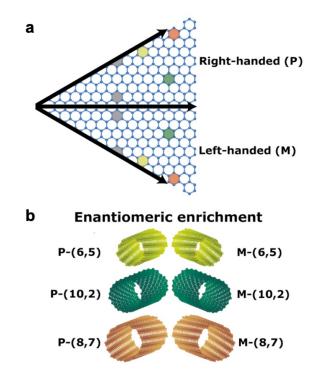

Despite their desirable mechanical, chemical, and thermal properties, SWCNTs are primarily utilized for their excellent charge transport properties. These electronic properties vary as a function of the chiral vector. Specifically, an (n,m) SWCNT will be semiconducting if n-m $\neq$  3z (where z is an integer) and metallic otherwise. Therefore, for samples consisting of a random distribution of chiral vectors, approximately 33% of the SWCNTs will be metallic and 67% will be semiconducting, with the semiconducting bandgap inversely proportional to the SWCNT diameter.<sup>9</sup> Semiconducting SWCNTs (s-SWCNTs) are preferred in most electronic applications, but often require semiconducting purity levels higher than 99% (Figure 1.2).<sup>1</sup> On the other hand, optoelectronic applications generally require enrichment of a single (n,m) chirality due to the diameter dependence of the SWCNT bandgap (Figure 1.3). As an additional degree of freedom, individual (n,m) SWCNTs are also defined by their handedness (M: left-handed, P: right-handed), which can be thought of as the two possible rolling directions for (n,m) SWCNT enantiomers. SWCNT handedness influences interactions with other chiral species (e.g., biomolecules) and circularly polarized light,<sup>21</sup> making it a crucial property for a number of advanced sensing applications (Figure 1.4).

**Figure 1.2** | **SWCNTs sorted by electronic type.** Illustration of electronic-type enrichment of raw SWCNTs. SWCNTs are separated into metallic and semiconducting species (**b**), with their corresponding chiral vectors highlighted in the chiral map (**a**). These SWCNT structures were generated using the TubeGen 3.4 web interface.<sup>19</sup> Reproduced with permission.<sup>20</sup> Copyright 2020, Wiley-VCH Verlag GmbH & Co. KGaA, Weinheim.

**Figure 1.3** | **SWCNTs sorted by chirality.** Illustration of monochiral enrichment of semiconducting SWCNTs. Semiconducting SWCNTs are separated by chirality (b), with their corresponding chiral vectors highlighted (a). These SWCNT structures were generated using the TubeGen 3.4 web interface.<sup>19</sup> Reproduced with permission.<sup>20</sup> Copyright 2020, Wiley-VCH Verlag GmbH & Co. KGaA, Weinheim.

**Figure 1.4** | **SWCNTs sorted by chirality and handedness.** Illustration of enantiomeric enrichment of monochiral SWCNTs. Monochiral SWCNTs are separated into right-handed (P) and left-handed (M) species (b) with their corresponding chiral vectors highlighted (a). These SWCNT structures were generated using the TubeGen 3.4 web interface.<sup>19</sup> Reproduced with permission.<sup>20</sup> Copyright 2020, Wiley-VCH Verlag GmbH & Co. KGaA, Weinheim.

#### **1.3 SWCNT direct growth**

Since the first demonstration of SWCNT synthesis in 1993,<sup>6</sup> researchers have explored the direct growth of SWCNTs with controlled structure (most commonly chirality, but also length and alignment). SWCNT growth depends on a broad number of synthetic parameters including substrate, temperature, pressure, and carbon source. However, it is generally believed that catalyst chemistry has the largest effect since chirality is dictated by initial nucleation during growth.<sup>10</sup> Most chirality-enriched direct growth methods can be classified into the following three categories: (1) carbonaceous molecular precursors; (2) metallic nanoparticles; (3) SWCNT fragments as growth seeds. We briefly discuss these three categories, and refer the reader to the

following comprehensive review articles for direct growth chirality control,<sup>10,22,23</sup> horizontal alignment,<sup>24,25</sup> catalyst design,<sup>26</sup> and epitaxy.<sup>27</sup>

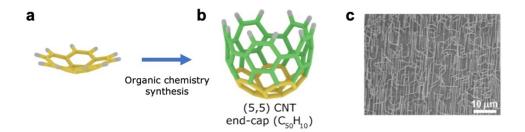

In direct growth using carbonaceous molecular precursors, synthetic organic chemistry is used to develop templates for SWCNT growth. Carbonaceous templates, such as end-cap precursors and carbon nanorings, are designed to have a molecular structure at their nucleation site that is identical to the target SWCNT chirality. In a notable demonstration of this strategy, corannulene molecules are used in the bottom-up synthesis of (5,5) SWCNT end-caps.<sup>28</sup> These molecules are then deposited on quartz substrates, and SWCNT growth is achieved using vapor phase epitaxy elongation. A schematic of the end-cap structure as well as a scanning electron microscope (SEM) image of the SWCNT growth are provided in Figure 1.5. Despite the atomically precise precursor design, characterization of the grown SWCNTs reveals a change in chirality during growth. This setback is representative of the challenges facing direct growth through carbonaceous molecular precursors, and highlights the need for further growth optimization. Even with these challenges, this methodology offers a number of promising advantages including metal-free catalyst growth and the potential for scalability through the use of high-throughput organic synthesis of identical templates.<sup>10,26,29</sup>

**Figure 1.5** | **SWCNT growth using molecular templates. a**, Structure of synthetic  $C_{20}H_{10}$  precursor for SWCNT growth. **b**, Structure of a  $C_{50}H_{10}$  molecular end-cap with a short segment of monochiral SWCNT following organic chemistry synthesis of precursor. **c**, SEM image of

SWCNTs grown using molecular end-cap templates on a quartz substrate. Reproduced with permission.<sup>28</sup> Copyright 2018, Wiley-VCH Verlag GmbH & Co. KGaA, Weinheim.

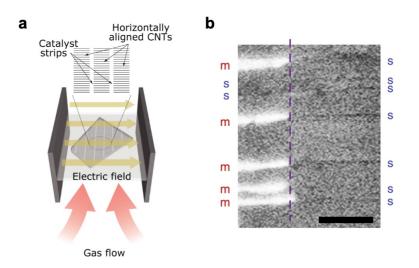

In direct growth using metallic nanoparticles, transition metals (e.g., Co, Fe, and Ni) are used due to their high catalytic activities for the dissociation of carbon precursors.<sup>23,30</sup> Metallic nanoparticle catalysts with carefully designed size and composition are formed on the growth substrate, after which SWCNT synthesis is achieved through carbon adsorption, nucleation, and elongation via chemical vapor deposition (CVD).<sup>26</sup> In one example of this method, CVD is performed on an ST-cut single quartz crystal with Fe catalyst strips. During synthesis, an alternating electric field is applied as shown in Figure 1.6, resulting in nucleation that produces horizontally aligned SWCNTs with 99.9% semiconducting purity.<sup>31</sup> Generally, the thermodynamics and kinetics of this growth method are highly sensitive to the catalyst properties, such that ideal conditions for chiral-selective growth require simultaneous control over a large number of growth parameters.<sup>22,24,25</sup> Consequently, advances to date have required extensive theoretical studies and/or significant experimental optimization.<sup>10,25</sup>

**Figure 1.6** | **SWCNT growth using electro-renucleation. a,** Diagram of an electro-renucleation system that utilizes metallic catalyst strips on a quartz crystal placed between two electrodes for controllable CVD growth using an alternating electric field. **b**, SEM image of SWCNTs

changing chirality during growth when electro-renucleation starts (dashed purple line). Bright and dark lines represent m-SWCNTs and s-SWCNTs, respectively. Reprinted by permission from Springer Nature: Nature Catalysis,<sup>31</sup> Copyright (2018).

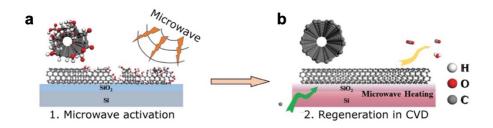

In direct growth using SWCNT fragments, open-ended SWCNTs serve as seeds that are elongated through epitaxial growth. Studies using this technique have confirmed that elongated SWCNTs maintain the original seed chirality. In one example of this growth method, SWCNT seeds are placed on a Si/SiO<sub>2</sub> substrate, and their growth edges are activated through exposure to microwave irradiation. Subsequent CVD growth from these activated SWCNTs results in synthesis with high regeneration efficiency and micron-scale elongation. An overview of this method is shown in Figure 1.7.<sup>32</sup> Further optimization of the microwave-assisted activation may help overcome the typical low yield and growth efficiency of SWCNT-seeded growth that is currently limited by spontaneous closure of the growth seed edge.<sup>27</sup> When coupled with recent advances in post-processing purification that will be delineated in the next section, this growth method has the potential to provide large-scale chirality enrichment.<sup>10,27</sup>

**Figure 1.7** | **SWCNT growth using microwave-assisted regeneration.** Schematic of microwave-assisted regeneration growth using irradiated SWCNT fragments (**a**) as growth seeds for regenerative growth using CVD (**b**). Reproduced with permission.<sup>32</sup> Copyright 2018, Wiley-VCH Verlag GmbH & Co. KGaA, Weinheim.

#### **1.4 SWCNT post-processing purification**

Despite the aforementioned advances in direct growth, post-processing purification is currently the more common route to SWCNT chiral enrichment. Due to the similarity in size between SWCNTs and biological macromolecules, many post-processing purification techniques draw inspiration from biotechnology separation methods.<sup>8</sup> Among the most successful post-processing techniques are: (1) dielectrophoresis; (2) polymer sorting; (3) aqueous two-phase extraction; (4) density gradient ultracentrifugation; (5) gel chromatography. We briefly discuss these five post-processing purification methods, and refer the reader to the following comprehensive reviews for electronic-type<sup>8</sup> and monochiral<sup>33,34</sup> enrichment. We also highlight that the following references<sup>33,34</sup> compare the scalability, applicability, enrichment levels, and performance of the post-processing purification methods discussed below. Post-processing purification for enantiomeric enrichment will be discussed in Section 2.3.

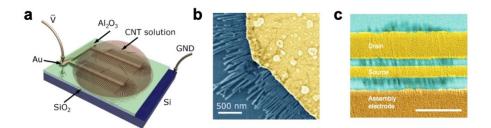

In dielectrophoresis, an alternating voltage is applied using planar electrodes to create a local, inhomogeneous electric field. Due to a difference in induced dipole moment between semiconducting and metallic species, s-SWCNTs suspended in solution near the electrodes selectively interact with the inhomogeneous electric field, resulting in preferential deposition. While early demonstrations of this method suffered from poor selectivity and non-uniform deposition,<sup>35</sup> near perfect alignment and uniform pitch have been more recently achieved through optimization of the fringing electric field.<sup>36</sup> A diagram of the dielectrophoresis process and an SEM image of the resulting uniform SWCNT arrays are provided in Figure 1.8. Electrophoretic methods can be scaled through the use of a dielectric medium (e.g., agarose gel electrophoresis) achieving yields up to 25%.<sup>37</sup> However, these scalable methods have only attained electronic-type purities up to 98%, have not demonstrated monochiral selectivity, and require additional post-

processing for the removal of agarose gels,<sup>34,38</sup> thus limiting the adoption of electrophoretic methods compared to other post-processing purification methods.

**Figure 1.8** | **SWCNT sorting using dielectrophoretic assembly. a,** Diagram of fringing-field assembly process using an alternating voltage input for self-limited pitch placement of semiconducting SWCNTs using fringing-field dielectrophoretic assembly. **b**, False-colored SEM image of assembled SWCNT arrays on an electrode. **c**, False-colored SEM image of FET using dielectrophoretic assembly to place s-SWCNTs as a channel between a drain and source electrode (500 nm scale bar). Reprinted by permission from Springer Nature: Nature Communications,<sup>36</sup> Copyright (2014).

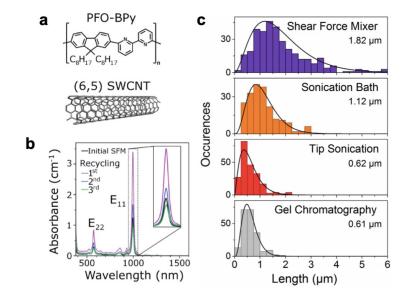

In polymer sorting, tailored polymers selectively interact with SWCNTs based on properties such as diameter, length, electronic type, and chirality. Although the precise sorting mechanism remains debatable, this selective interaction creates a dispersion that can be separated from a bulk mixture using solution processing, most often through centrifugation.<sup>39</sup> In a notable example of polymer sorting, high-speed shear force mixing is used to disperse poly[(9,9-dioctylfluorenyl-2,7-diyl)-*alt-co*-(6,6'-[2,2'-bipyridine] )] (PFO-BPy) and SWCNTs in a toluene solution. This polymer produces large volumes of nearly monochiral SWCNT dispersions, with s-SWCNT purity above the optical characterization detection limit (>99%) and (6,5) SWCNT content above 84%.<sup>40</sup> Figure 1.9 shows the structure of PFO-BPy and (6,5) SWCNTs, as well as the optical absorption spectra of dispersions after sequential recycling of unwrapped material. A number of other distinct sorting polymers with unique functionality have been developed, including polymers that can achieve ultrahigh purity electronic-type enrichment,<sup>8,41</sup> and polymers

that can be recycled to minimize production costs.<sup>42,43</sup> Polymer sorting remains an effective method for state-of-the-art electronic-type enrichment, achieving semiconducting purities above 99.9% and yields above 20%.<sup>15,34,41,42</sup> Although monochiral enrichment purities are significantly lower (50-84%), polymer sorting is compatible with large-scale and iterative solution-processing methods,<sup>33,40,44</sup> suggesting that it may be able to achieve higher levels of monochiral enrichment.

**Figure 1.9** | **SWCNT sorting using polymer-wrapping. a**, Structure of the sorting copolymer PFO-BPy and the target monochiral (6,5) SWCNT. **b**, Evolution of the absorption spectra of (6,5) SWCNT-copolymer dispersions after sequential recycling of unwrapped material from selective dispersion of (6,5) SWCNTs using high-speed shear force mixing. **c**, Length distribution of (6,5) SWCNTs using shear force mixing, bath sonication, tip sonication and gel chromatography. Reprinted from <sup>40</sup>, Copyright (2016), with permission from Elsevier under CC BY NC ND.

In aqueous two-phase extraction (ATPE), two water-soluble polymers are mixed, spontaneously creating two distinct immiscible phases. Using the poly(ethylene glycol) (PEG) / dextran (DX) system, the immiscible phases allow for the selective extraction of SWCNT species due to their different affinities for SWCNTs based on diameter, length, electronic-type, chirality,

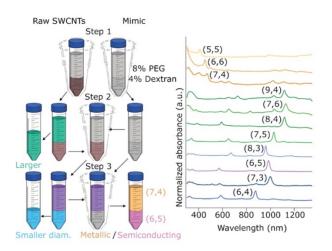

and surface chemistry (e.g., surfactants). In a notable demonstration, ATPE using the PEG/DX system achieved monochiral separation of SWCNTs in three processing steps, thus enabling the separation of 11 small-diameter SWCNT chiralities using amphiphilic surfactants.<sup>45</sup> A schematic of the processing steps and the resulting optical absorption spectra of the separated SWCNT chiralities are provided in Figure 1.10. ATPE has also been used for the separation of up to 15 different SWCNT chiralities using specific DNA sequences for partitioning<sup>46</sup> with exceptionally high fidelity.<sup>47</sup> ATPE can achieve state-of-the-art semiconducting purities above 99.5%<sup>48</sup> and monochiral enrichment purities above 85%.<sup>49</sup> Consequently, ATPE has the potential for high scalability, although efficient removal of impurities from the isolated SWCNT species remains an open challenge.<sup>8,34</sup>

**Figure 1.10** | **SWCNT sorting using ATPE.** Separation of SWCNT chiral species using threestep ATPE. (left) Schematic of the ATPE procedure for the separation of two monochiral species. (right) Absorption spectra of 11 extracted SWCNT monochiral species. Reprinted with permission from <sup>45</sup>. Copyright 2019 American Chemical Society.

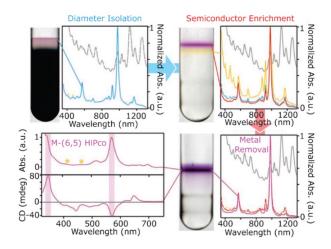

In density gradient ultracentrifugation (DGU), the buoyant density of SWCNT species is controlled using selective dispersants. SWCNTs are then separated into different layers through the use of a density gradient medium and ultracentrifugation.<sup>9</sup> While initial efforts enabled DGU

separation by SWCNT electronic-type and diameter,<sup>50</sup> subsequent work on orthogonal iterative DGU resulted in nearly monochiral separation.<sup>51</sup> Examples of separation by diameter, electronic type, and chirality through orthogonal iterative DGU are illustrated in Figure 1.11. Due to the high selectivity and iterative nature of DGU, semiconducting purities above 99%<sup>51,52</sup> and monochiral enrichment purities above 88%<sup>53</sup> have been achieved in a manner that is readily scalable for industrial applications.<sup>8,34</sup>

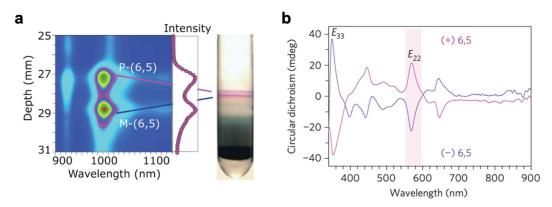

**Figure 1.11** | **SWCNT sorting using DGU.** Optical absorbance spectra, circular dichroism (CD) characterization, and optical photographs showing multiple DGU iterations for electronic-type, monochiral, and enantiomeric enrichment. Reproduced with permission.<sup>51</sup> Copyright 2011, Wiley-VCH Verlag GmbH & Co. KGaA, Weinheim.

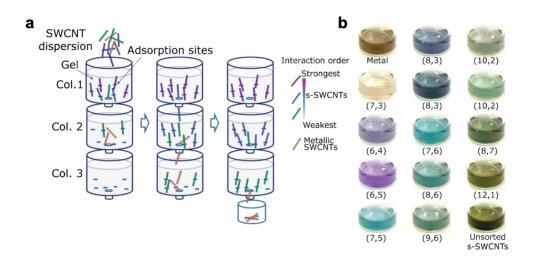

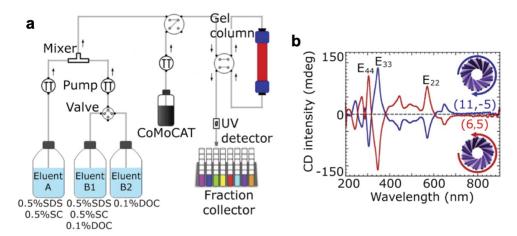

In gel chromatography (GC), SWCNT dispersions are separated as they pass through gel columns by exploiting the selective interactions between SWCNTs species and various stationary phases. Through the use of different dispersants and gels, GC can separate SWCNTs by diameter, length, electronic type, and chirality.<sup>8</sup> In one notable example, the use of a single surfactant (i.e., sodium dodecyl sulfate) and multiple gel columns enabled the GC separation of 13 SWCNT chiralities with purities in the range of 46-93%.<sup>54</sup> A schematic of this GC method and photographs of the separated SWCNT species are shown in Figure 1.12. The compatibility of GC with iterative

processing has allowed electronic-type enrichment purity up to 99.9%.<sup>55</sup> GC using ion exchange with single-stranded DNA (ss-DNA) is also capable of sorting SWCNTs by diameter, electronic type, and chirality.<sup>34,56</sup> Since GC has demonstrated large-volume electronic-type and monochiral enrichment with high yields and purity levels,<sup>57</sup> it also has high potential for industrial-scale applications.

**Figure 1.12** | **SWCNT sorting using gel chromatography. a**, Schematic of single-surfactant multicolumn gel chromatography that enables separation of SWCNT monochiral species. **b**, Photographs of 13 separated monochiral species. Reproduced from<sup>54</sup>, licensed by CC BY-NC-SA 3.0.

Chapter 2: Carbon nanotube electronic devices

# 2.1 Electronic applications of semiconducting SWCNTs

#### **2.1.1 Flexible smart devices**

### 2.1.1.1 Additive manufacturing of flexible SWCNT devices

A key advantage of SWCNTs, in addition to excellent charge transport properties, is their solution processability that enables the use of additive manufacturing techniques, most notably aerosol and inkjet printing. Combined with low-temperature processing and their ultrathin nature, SWCNT-based devices enable flexible computing applications with negligible performance dependence on mechanical deformation.<sup>2</sup> In this section, we briefly discuss a number of key advances in the additive manufacturing of SWCNT devices.

The most common formulations for SWCNT inks employ aqueous surfactant solutions, polymer wrapping, and select organic solvents, which closely follow dispersion strategies in post-processing purification methods.<sup>58</sup> Although not as important for aerosol jet printing, ink viscosities in the ranges of 40 - 2,000 centipoise and 1 - 20 centipoise are required for gravure and inkjet printing, respectively. SWCNT inks are most commonly used to deposit randomly oriented SWCNT networks with feature sizes larger than 5 µm, where uniformity in SWCNT density is critical. Therefore, printing is often aided by surface modification methods,<sup>59,60</sup> where inks are designed to optimize dispersion uniformity and wettability.<sup>3</sup> We refer the reader to the following comprehensive review for further information on SWCNT-based dispersions and printing techniques for flexible SWCNT devices.<sup>3</sup>

In aerosol jet printing, s-SWCNTs inks are aerosolized and printed through a small nozzle using a sheath of inert gas. Although studies generally focus on the charge transport properties of aerosol jet printed s-SWCNT channels, printed contacts also play an important role in overall FET performance. Fully aerosol jet printed devices have been studied using different contact geometries (e.g., top, bottom, and double) and contact materials including metallic (e.g., Au and Ag) nanoparticles and metallic SWCNTs (m-SWCNTs). It has been found that m-SWCNTs have the lowest contact resistance, especially in the double contact geometry.<sup>59</sup> The performance of an allprinted SWCNT thin-film transistor (TFT) has also been characterized, using s-SWCNT ink for semiconducting channel, nanoparticle ink for the electrodes, the Ag and poly(vinylphenol)/poly(methyl silsesquioxane) (PVP/pMSSQ) for the gate dielectric. With a topgated structure on a Kapton film, ambient-stable p-type TFTs have been realized with negligible hysteresis and minimal performance variation over 1,000 bending cycles.<sup>61</sup>

In inkjet-printing, s-SWCNTs inks are formulated such that ink droplets can be ejected by a nozzle with precise control over the jetting speed, droplet size, and droplet shape. In one demonstration, SWCNT TFTs were fabricated on flexible polyimide substrates using s-SWCNT ink for the semiconducting channel and Ag nanoparticle ink for the electrodes. The gate dielectric of Al<sub>2</sub>O<sub>3</sub> was deposited using atomic layer deposition (ALD), resulting in a change of the TFT transfer characteristics from p-type to ambipolar. This ambipolarity enabled complementary-like ICs including a NAND gate, a NOR gate, and a 3-stage ring oscillator (RO).<sup>62</sup> The RO structure operated continuously for 83 hours with minimal performance variation<sup>62</sup> and allowed the sensing of polar vapors (e.g., acetone),<sup>63</sup> demonstrating the high stability and functionality of this inkjet printing scheme. Although most inkjet-printed SWCNT TFTs have channel lengths larger than 10 µm due to limitations in printing resolution, the fabrication of a fully inkjet-printed TFT with a sub-micron channel length has also been achieved. In this case, a hydrophobic, self-assembled monolayer was applied to an Au nanoparticle electrode to repel a subsequent overlapping printed electrode. This second electrode thus retracts from the functionalized surface, creating a submicron gap of ~400 nm between the two electrodes after printing. Using an ion gel as the gate dielectric, these highly-scaled TFTs achieve simultaneously large ON currents of ~4.5  $\mu$ A· $\mu$ m<sup>-1</sup>, high ON/OFF ratios of ~10<sup>5</sup>, and low-voltage operation (V<sub>DS</sub> = -0.1 V and V<sub>G</sub> = -1.5 V).<sup>64</sup> While high-throughput, high-resolution printing remains challenging, the self-aligned capillary-assisted lithography for electronics (SCALE) method provides a path to overcome this bottleneck. SCALE combines inkjet printing with imprint lithography by depositing inks into patterned imprints on a flexible substrate, such that the inks flow from ink reservoirs to narrow cavities through capillary forces. High-resolution SWCNT TFTs have been achieved by using inks for the channel, electrodes, and gate dielectric, including s-SWCNT ink for the semiconducting channel.<sup>65</sup>

Other studies have demonstrated shape-controlled substrates,<sup>66</sup> intrinsically stretchable transistors,<sup>67</sup> and high-throughput fabrication using a photosensitive dry film.<sup>68</sup> In shape-controlled substrates, SWCNT flexible electronic devices are fabricated on a bilayer of polyimide and a shape memory polystyrene structure. These structures are formed into free-standing three-dimensional shapes through structural pre-programming, and can also conformably wrap around irregularly shaped objects through rapid heating. Embedded SWCNT TFTs, sensors, and memory devices in these structures show no significant performance degradation when mechanically deformed.<sup>66</sup> Intrinsically stretchable, all-carbon transistors have also been achieved using transfer printing of a s-SWCNT channel, m-SWCNT electrodes, and a non-polar elastomer dielectric and substrate. A non-polar dielectric is used to minimize hysteresis and stress bias effects in the transistors, while optimized SWCNT source electrodes help achieve transistor performance comparable to conventional SWCNT transistors on rigid substrates.<sup>67</sup> In a high-throughput fabrication approach,

a photosensitive dry film (DuPont Riston MX9010) is laminated on a flexible polyethylene naphthalate (PEN) substrate using roll-to-roll (R2R) technology. The resulting film is then used as a negative photolithography resist layer, which enables a 5 μm pattern resolution over the area of an A5-paper-sized PEN substrate through conventional UV exposure. Flexible and transparent all-carbon TFTs are then fabricated using a poly(methyl methacrylate) (PMMA) dielectric layer and SWCNTs for the channel and electrodes. TFTs and inverters fabricated with this scheme have attained high performance, reproducibility, and uniformity over the entire PEN substrate, highlighting the potential of this manufacturing technique in future low-cost, R2R fabrication of SWCNT computational devices.<sup>68</sup>

### 2.1.1.2 Flexible SWCNT analog and digital devices

SWCNTs provide a number of unique advantages over other semiconducting materials that are used for TFTs. Due to their sp<sup>2</sup> bonding and high carrier mobilities, SWCNT TFTs possess high drive current with long-term ambient stability. Moreover, their ultra-thin body and compatibility with common printing methods enable low-cost TFTs on flexible substrates with performance that is resilient to mechanical deformation. However, SWCNT TFT applications must still consider the effects of ink chemistry, network composition, and post-processing conditions in order to exploit these advantages. In particular, high-performance SWCNT TFTs on rigid substrates require carefully optimized device processing to reduce the effects of ambipolar transport and device-to-device variability. Key performance metrics for SWCNT TFT devices include ON/OFF ratio (typically greater than 10<sup>3</sup>), carrier mobility (typically above 10 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>), and ON current (typically above 10 µA•µm<sup>-1</sup>). We refer the reader to the following comprehensive reviews for further information on key device properties and requirements for printed<sup>3</sup> and highperformance<sup>4</sup> SWCNT TFTs.

Flexible smart devices require high-performance analog and digital components that can be fabricated on flexible substrates and properly operate under mechanical deformation.<sup>4,8,10</sup> Towards this end, several studies have established the performance and computational capabilities of flexible SWCNT devices through fabrication optimization. For further information on key device properties and requirements for SWCNT TFTs, we refer the reader to the following comprehensive review.<sup>4</sup> In a key demonstration of channel scalability, inkjet-printed SWCNT network channels have been used to fabricate R2R compatible transistors with channel lengths of 150-250 nm. These devices achieve ON/OFF ratios of  $\sim 10^3$ , transconductance (g<sub>m</sub>) greater than 150 µS·µm<sup>-1</sup>, and a mobility as high as 209 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>.<sup>69</sup> Beyond traditional length scaling challenges, flexible SWCNT analog and digital electronics must demonstrate simultaneous computational complexity and minimal performance dependence on mechanical deformation. For example, SWCNTs have been used to fabricate capacitors, logic gates, and charge-trap floating gate memory units on flexible polyimide substrates using standard CMOS processing. These analog and digital devices use serpentine connections and neutral plane layouts to conformally laminate onto human skin with mechanical deformation (e.g., stretching, poking, and compression) leading to minimal performance variation.<sup>70</sup> In order to realize the full potential of possible deformation in flexible SWCNT electronics, s-SWCNT p-type devices are fabricated on a 1.4 µm poly(ethylene terephthalate) (PET) film using standard CMOS fabrication. These highperformance TFTs have been crumpled, bent down to ~40 µm radius of curvature, and compressively strained by 67% with negligible performance variation due to their ultrathin and

lightweight (3 g·m<sup>-2</sup>) nature. Similarly, fabricated p-type based logic gates maintain their functionality when compressively strained by 33%.<sup>71</sup>

While most flexible SWCNT devices have microsecond-scale stage delays and only use ptype TFTs, these two limitations can be overcome by using ultrahigh purity (>99.9%) s-SWCNT solutions and a scalable n-type doping process. To n-type dope s-SWCNT TFT devices, a thin 2 nm layer of Al is deposited on a bottom-gate/top-contact structure followed by a 40 nm Al<sub>2</sub>O<sub>3</sub> encapsulation layer grown using ALD. The resulting n-type doping enables flexible devices with current densities over 17  $\mu$ A· $\mu$ m<sup>-1</sup>, ON/OFF ratios of ~10<sup>6</sup>, and mobilities of ~50 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. Additionally, flexible logic gates and ROs have been fabricated including a 5-stage RO with an oscillation frequency as high as 17.6 MHz,<sup>72</sup> demonstrating that state-of-the-art SWCNT devices on flexible substrates can achieve metrics that are competitive with SWCNT devices on conventional rigid substrates.

Beyond SWCNT TFTs and digital logic gates, other important functional components have been demonstrated, such as radiation-hard devices,<sup>73,74</sup> random number generators,<sup>75</sup> shiftregisters, and tunable gain amplifiers.<sup>15</sup> In radiation-hard SWCNT devices, *in situ* and *in operando* total ionization dose (TID) effects have been measured for CMOS inverters fabricated using s-SWCNT random network channels, molecular dopants, and an Al<sub>2</sub>O<sub>3</sub> encapsulation layer. While the n-type transistors were found to be the most TID-sensitive component, these inverters are TIDhard under dynamic bias operation.<sup>73</sup> Similarly, radiation-hard static random access memory (SRAM) cells fabricated using doping-free processing can function up to a 2.2 Mrad TID, establishing the capability of using SWCNT-based ICs in extreme environments.<sup>74</sup> In another study using a molecular doping and encapsulation method, a SWCNT SRAM cell has been operated as a true random number generator through the digitization of random thermal noise. The generated bit output is confirmed to be random by established statistical tests for randomness, demonstrating the realization of a ubiquitous security primitive crucial to future SWCNT-based applications.<sup>75</sup> Using ultrahigh purity (99.997%) s-SWCNTs, a pseudo-CMOS circuit design, and state-of-the-art processing, low-voltage 8-stage shift registers operating at 50 kHz and tunable gain amplifiers with a gain of 1,000 at 20 kHz have also been fabricated,<sup>15</sup> showing the extensive functional capabilities of flexible SWCNT digital and analog devices.

### 2.1.1.3. SWCNTs in flexible display technologies

SWCNTs TFTs are expected to provide superior performance as drivers for display technologies due to their high current capacity, ultrathin size, optical transparency, and compatibility with scalable, low-temperature fabrication.<sup>76</sup> We briefly discuss a number of key demonstrations of the integration of SWCNT devices in flexible displays and refer the reader to the following comprehensive review on the fabrication, design, and integration of flexible smart display technologies.<sup>77</sup>

In one study, solution-based printing was used to create optically transparent SWCNT TFTs with stretchable electrodes and an elastomeric dielectric. These TFTs achieved high electrical performance that is retained at 50% strain and after 500 cycles at 20% strain, thereby allowing them to drive white organic light-emitting diode (OLEDs) at up to 30% strain.<sup>78</sup> However, practical display applications require the integration of TFT drivers in multi-pixel displays. Towards this end, SWCNT TFT drivers using polymer-sorted s-SWCNTs have been fabricated, showing an average mobility of 13 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and an ON/OFF ratio of over 10<sup>6</sup>. These

high-performance SWCNT TFTs have been monolithically integrated with polymer-dispersed liquid crystals (PDLC) in an active matrix display, allowing a fully functioning seven-segment display to be achieved.<sup>79</sup>

In order to further confirm the uniformity and yield of SWCNT TFTs in larger displays, SWCNT TFT drivers have also been monolithically integrated in a flexible  $64 \times 64$  pixel activematrix OLED display (AMOLED). Through a heat pretreatment and cleaning process for the flexible PEN substrate, uniform display brightness and a high pixel yield (99.93%) are achieved. Over 8,000 characterized SWCNT TFTs show an average ON/OFF ratio of ~10<sup>7</sup> and a carrier mobility of 16 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, with both metrics showing a standard deviation of less than 7% across the entire display.<sup>80</sup> Overall, these advances confirm the compatibility of SWCNT TFT drivers with flexible display technologies. SWCNT-based active-matrix electrochromic displays have also been realized,<sup>81</sup> validating the feasibility of integrating SWCNTs into a variety of display technologies.

#### 2.1.1.4 SWCNTs in sensing technologies

Although SWCNTs have high chemical stability due to their stable sp<sup>2</sup> bonding, their high surface area makes them sensitive to non-covalent environmental interactions. More specifically, polar adsorbates result in charge redistribution within SWCNTs, affecting their charge transport properties. This principle is exploited when using SWCNTs as the active element for chemical and biological sensing, most commonly chemiresistive sensors and FET-based sensors. To further enhance sensing performance, SWCNTs are often functionalized to increase sensitivity, and multiplexed sensing is utilized for increased selectivity.<sup>3</sup> Early studies showed that these sensing

properties of SWCNTs could be exploited in molecular sensing applications,<sup>13</sup> driving the development of an entire field of research dedicated to the use of SWCNTs in large-scale, high-sensitivity sensors. We briefly discuss recent progress in SWCNT sensors, and refer the reader to the following comprehensive review of SWCNT-based sensor systems.<sup>3</sup>

Similar to their use as active-matrix drivers in display technologies, one application of SWCNTs for sensing technologies is as flexible active-matrix backplanes integrated with other sensing materials. In one demonstration, a  $20 \times 20$  active-matrix was fabricated through R2R gravure printing using a flexible PET substrate, a s-SWCNT semiconducting channel, Ag nanoparticle ink electrodes, and a BaTiO<sub>3</sub> nanoparticle-based ink dielectric. The fabricated devices are a significant milestone in R2R printing due to their simultaneous high device yield above 98% and high resolution of 9.3 points per inch (ppi) along an entire 15 m PET roll. A pressure-sensitive rubber (PSR) film was then laminated on these devices in order to modulate their drain current when pressure is applied to the matrix, creating a functioning multi-touch pressure sensor.<sup>82</sup> This system shows negligible performance variations when bent down to a radius of curvature of ~1.85 cm.<sup>83</sup> In another study, a 16 × 16 active matrix using SWCNT TFTs and PSR pixels was fabricated through standard CMOS processing on a flexible polyimide substrate. The individual TFT devices achieved a high ON/OFF ratio of over 10<sup>5</sup>, a high mobility of 17 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, and nearly 99% yield over the entire 4-inch fabrication area. These devices achieve low-voltage operation with simultaneous fast response (< 30 ms) and high spatial resolution (~ 4 mm), and are capable of accurately sensing objects when bent down to a radius of curvature of 60 mm.<sup>84</sup> Overall, these advances present a path towards the realization of complex, large-area sensors, such as SWCNTbased "electronic skin" (e-skin) that is capable of mechanically conformal, multiplexed sensing.

For molecular sensing, FETs using single suspended SWCNTs have been characterized *in situ* when exposed to ionized gases. These devices show quantized and discrete increases in resistance due to SWCNT carrier depletion by single adsorption events of positive gas ions.<sup>85</sup> In another demonstration, a highly optimized fabrication strategy was employed to develop SWCNT-based H<sub>2</sub> sensors with sub-ppb detection. In particular, high-purity s-SWCNTs sorted by poly[9-(1-octylonoyl)-9H-carbazole-2,7-diyl] (PCz) were used to create a large semiconducting channel, which was then functionalized with Pd nanoparticles for the capture of H<sub>2</sub>. A scalable, resistor-type fabrication design with Ti Schottky barrier contacts enabled detection of H<sub>2</sub> down to 890 ppb at room temperature and 89 ppb at 100 °C,<sup>86</sup> demonstrating that high-sensitivity sensors can be realized using high-throughput sensor fabrication methods.

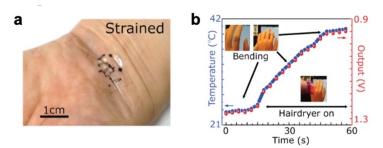

Beyond molecular sensing, SWCNT-based humidity and temperature sensors have also been achieved. For example, SWCNT-based humidity sensors have been realized through the optimization of SWCNT CMOS FETs utilizing Pd (Sc) contacts for high-performance p-type (ntype) devices. These humidity sensors were fabricated on an ultrathin plastic foil that integrates a humidity-sensitive polymer variable resistor with a SWCNT three-stage CMOS RO functioning as a frequency-modulating signal processing unit. These devices consume minimal power (< 60  $\mu$ W) and can be attached to human skin to detect relative humidity (RH) changes, such as the transition from dry (41% RH) to sweaty skin (84% RH).<sup>87</sup> Temperature sensors have also been fabricated using unsorted-SWCNT electrodes, high purity s-SWCNT channels, and a non-polar styrene-ethylene-butadiene-styrene (SEBS) film as both the substrate and dielectric. Most notably, different circuit configurations were explored, resulting in static differential and dynamic differential circuits for temperature sensing with sensitivities in the range of -20 mV·°C<sup>-1</sup>. Figure 2.1 shows a photograph of a temperature sensor conformally wrapped around a human wrist during bending and its stable temperature sensing operation when undergoing bending cycles. Overall, these temperature sensors achieve a low measurement error of  $\pm 1^{\circ}$ C under uniaxial strain as high as 60%,<sup>88</sup> showing that SWCNT transistors can be used for both the analog and sensing electronics of complex environmental signals.

**Figure 2.1** | **Stretchable temperature sensing circuit. a**, Optical photograph demonstrating skin-like conformity of a SWCNT sensor laminated onto a wrist during bending. b, Temperature sensor in stable operation during bending and heating while attached to a rubber prosthetic hand. Reprinted by permission from Springer Nature: Nature Electronics,<sup>88</sup> Copyright (2018).

In two other notable studies, time-based sensor interfaces<sup>89</sup> and transfer on biological surfaces<sup>90</sup> have been demonstrated. Briefly, time-based sensor interfaces enable robust, low-power sensing that can be readily integrated with traditional digital systems. Using 32 nm SWCNT technology (i.e., 32 nm minimum feature size), an integrated time-based IR sensor with a low supply voltage of 2 V has been shown to operate at ~100 kHz with a low power consumption of 130 nW.<sup>89</sup> In another study, the bio-integration capabilities of flexible SWCNT-based electronics were demonstrated by fabricating high-performance SWCNT devices on a transferable substrate. Through a sacrificial layer approach, these devices have been successfully transferred to several irregular biological surfaces including a human wrist, a biodegradable polymer, and a curved plant

leaf. The devices transferred onto the curved plant leaf exhibit low power consumption and high uniformity with negligible performance dependence on leaf curvature.<sup>90</sup> These two studies show the diversity of SWCNT-based sensor integration, highlighting the potential of SWCNTs in next-generation, energy efficient, conformable sensor systems.<sup>91</sup>

# 2.1.1.5 Integration of flexible SWCNT devices for smart systems

As covered in the previous sections, flexible SWCNT digital, analog, display, and sensor devices have been realized using scalable manufacturing methods. Therefore, monolithic integration of these components could provide a novel material platform for next-generation flexible smart devices.<sup>2,5</sup> Towards this end, a number of SWCNT-based integrated systems have been realized that exploit complementary sensing, computational, and manufacturing advantages. We briefly discuss recent progress in these integrated systems, and refer the reader to the following comprehensive review on SWCNT-based flexible electronic systems.<sup>2</sup>

Interactive, pressure-sensitive systems have been realized through the heterogeneous integration of multiple SWCNT electronic components. For instance, a user-interactive e-skin has been fabricated on a polyimide substrate by integrating a  $16 \times 16$  SWCNT active-matrix with OLED/PSR pixels. The PSR increases in conductivity as pressure is applied to the active matrix, resulting in instantaneous pressure mapping through light emission and pressure magnitude feedback through the emitted light intensity.<sup>92</sup> In another example, fully-printed SWCNT TFTs have been integrated with a microcontroller and a Bluetooth communication chip to create a flexible environmental pressure sensor that is capable of wireless data transmission. Environmental pressure on the SWCNT TFT sensor modulates the transconductance by 48.1

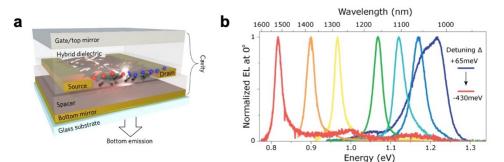

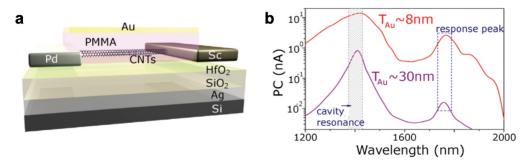

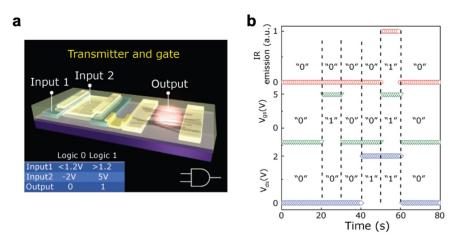

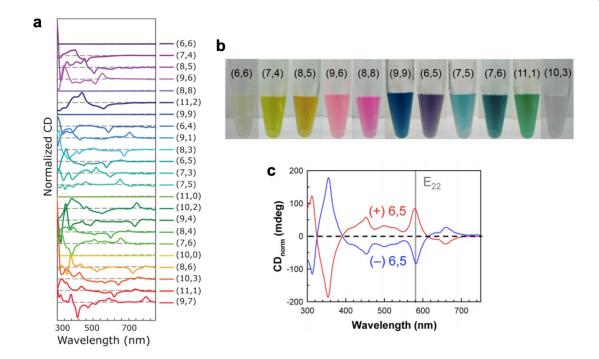

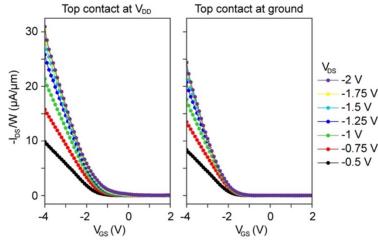

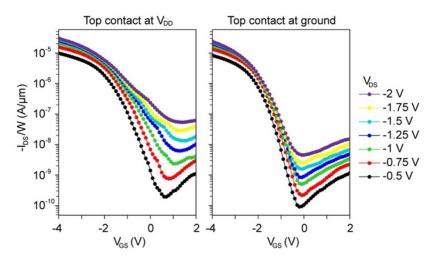

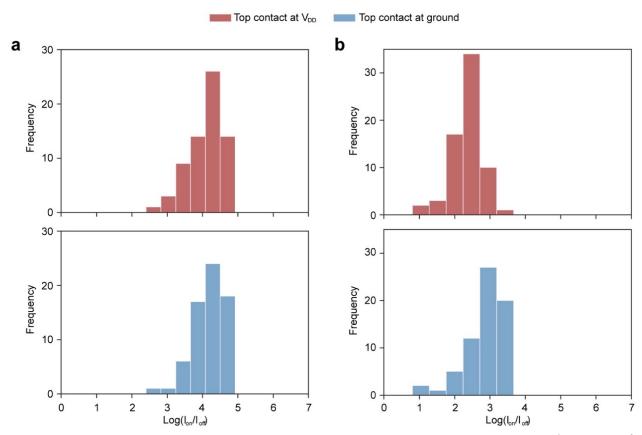

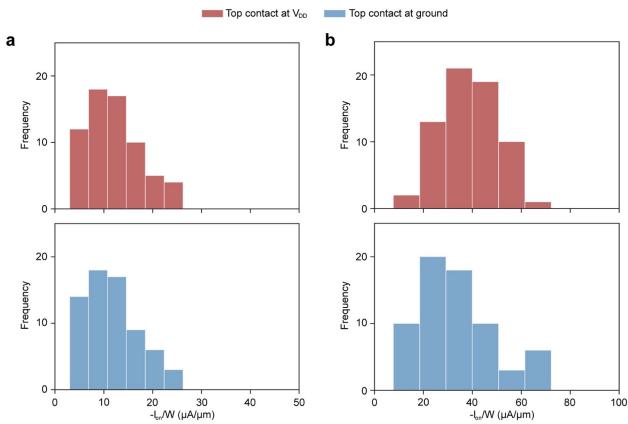

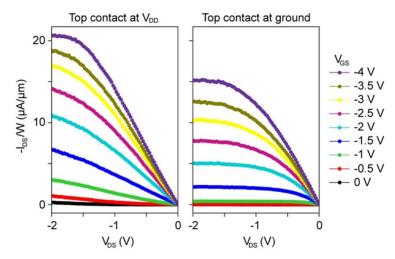

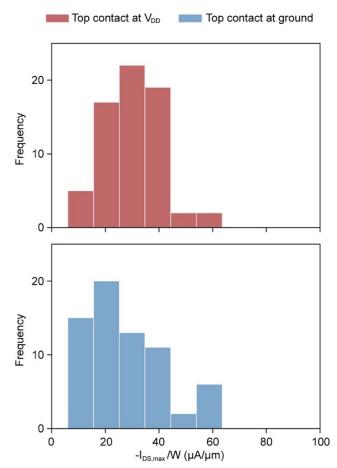

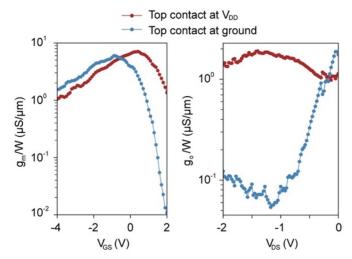

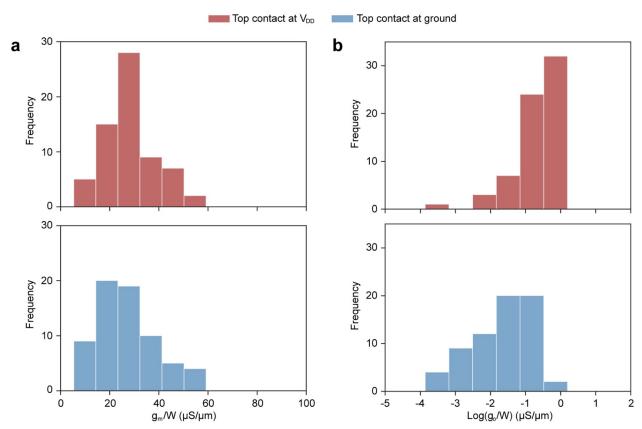

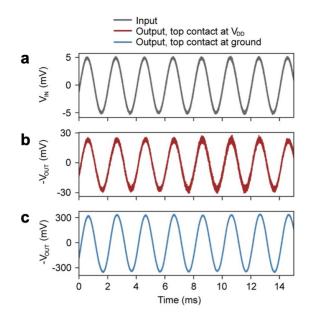

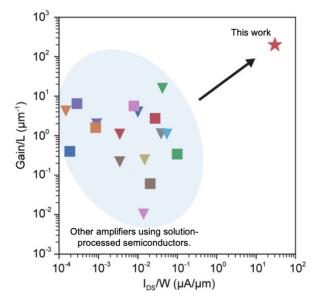

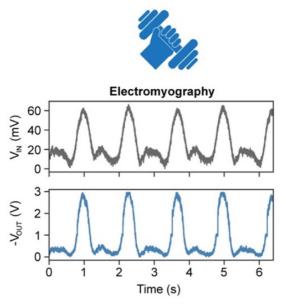

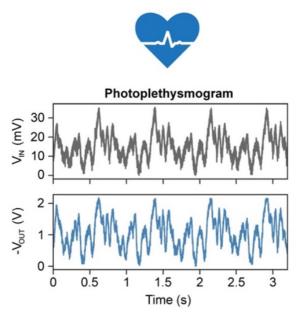

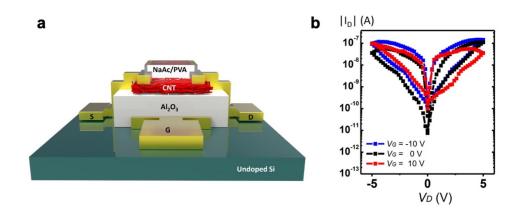

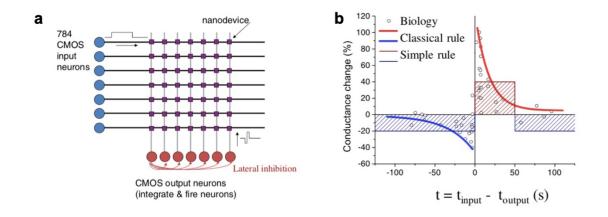

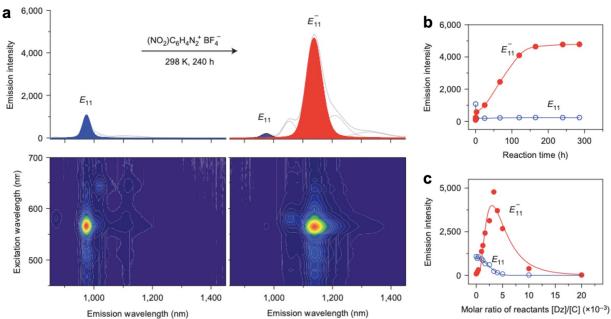

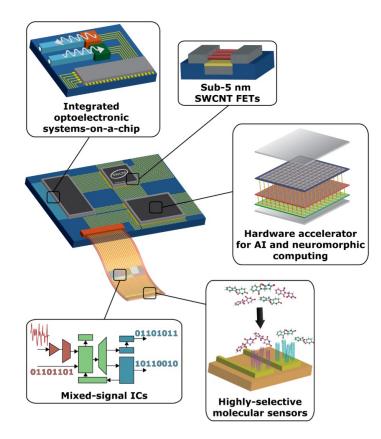

$pS \cdot PSI^{-1}$  over a range of 0 - 42 PSI, such that this sensor is used as a flexible, low-cost tire pressure sensing system. This system has been further integrated with another material thickness sensing unit to create a smart tire sensor for real-time tire pressure and tread depth monitoring.<sup>93</sup>